概述

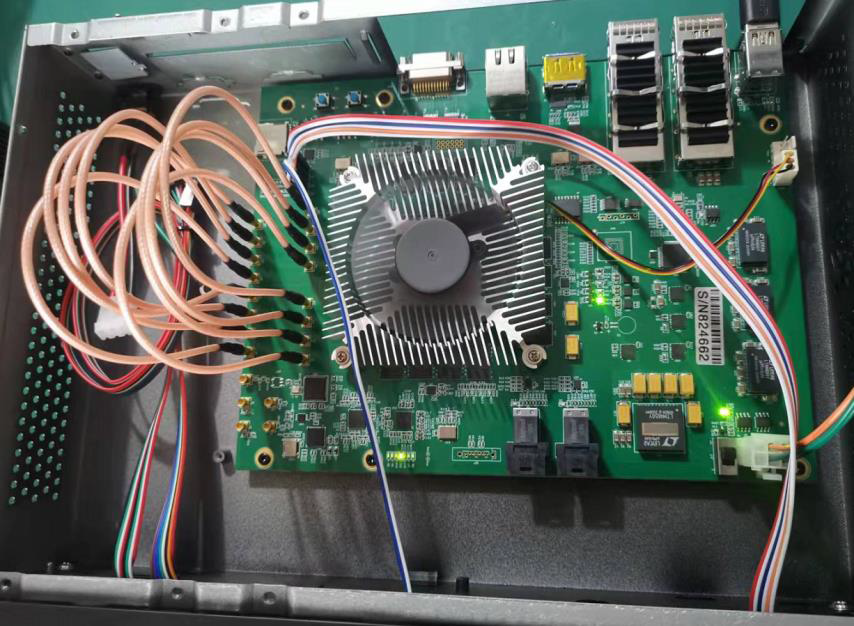

FACE-RFSOC-A自适应射频开发平台,是FACE系列新一代的产品。 平台搭载有16nm工艺的Zynq® UltraScale+™ RFSoC系列主器件。该器件集成数千兆采样RF数据转换器和ARM® Cortex®-A53处理子系统和UltraScale+可编程逻辑,是一款单芯片自适应射频平台。 板卡是标准MATX版型的RFSOC平台,平台板载有丰富计算资源的同时还具备有非常丰富的外设接口:QSFP28、U.2 NVMe、以太网、USB3.0等。该平台是无线电、雷达等高端射频应用场景下的理想开发/部署平台。

RF Analyzer 是XILINX提供的一套上位机软件,它为用户提供了一种简单快速的方法来评估 Zynq® UltraScale+™ RFSoC 中 RF-ADC 和 RFDAC 的性能的方法。

本文中,我们将会全面介绍FACE-RFSOC-A板卡各个接口外设的测试,并且使用XILINX RF Analyzer软件完成对FACE-RFSOC-A板卡射频部分的测试,包括板卡ADC/DAC配置以及MTS配置等,并对ADC和DAC平坦度、同步性能以及通道间的串扰情况进行测试。

一、平台接口外设测试

FACE-RFSOC-A板卡外设接口外设(除AD/DA以外)主要包含:

1. ZU ARM PS侧的:USB接口、USB-UART接口、以太网接口、SD卡接口、DP显示接口、QSPI Flash存储、PS DDR4存储等;

2. ZU PL逻辑侧的:QSFP28 100G高速光接口、PL DDR4 存储、J30J GPIO扩展接口、U.2 NVME SSD接口、拨码开关与LED灯等;

测试报告将通过若干FPGA工程来对上述接口外设进行测试,其中操作系统测试工程将覆盖上述大部分接口外设的功能。

平台各接口测试目录

二、RF Analyzer软件

1、RF Analyzer介绍

RF Analyzer 提供了一种简单快速的方法来评估 Zynq® UltraScale+™ RFSoC 中 RF-ADC 和 RFDAC 的性能。 RF Analyzer 要求主机上安装 2020.1 硬件服务器(或更高版本)或 Vivado® Design Suite(2020.1 或更高版本)。 下载BIT流前请根据实际硬件设计确保外部时钟稳定。 如果转换器 IP 启动时没有可用的有效时钟,则相应的转换器图块可能会显示错误。

2、RF Analyzer安装

双击阿吉毕科技提供的软件安装包;

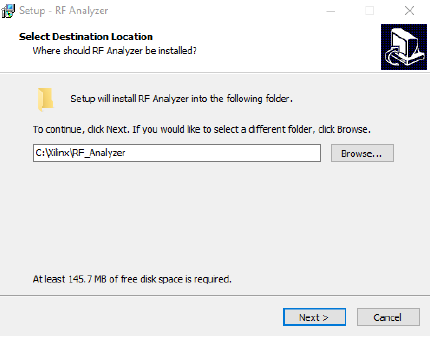

选择合适的安装路径;

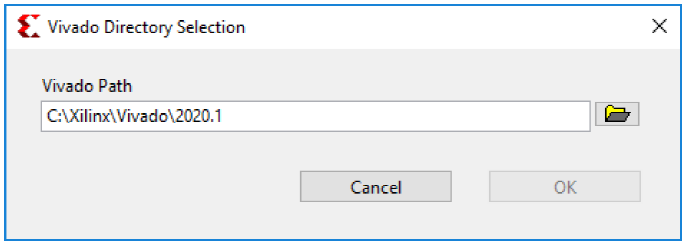

安装后,需要指定VIVADO安装路径。

三、AD/DA同步性能测试

1、ADC同步采集测试

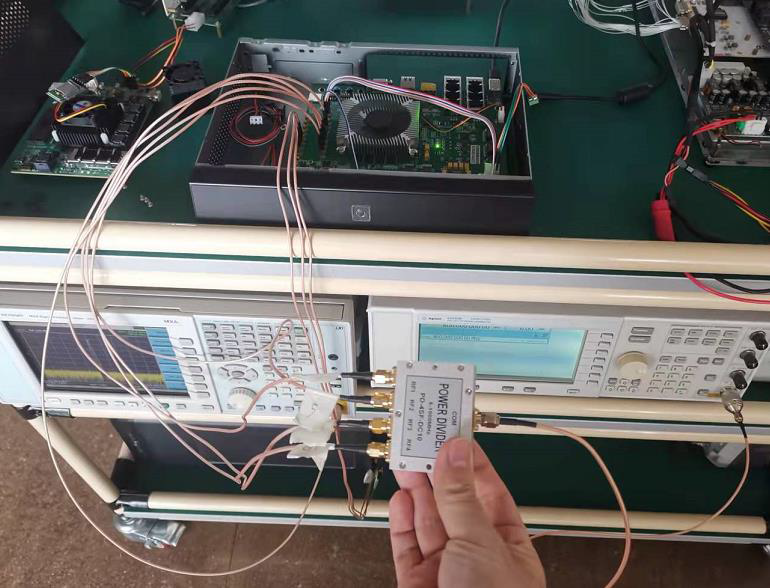

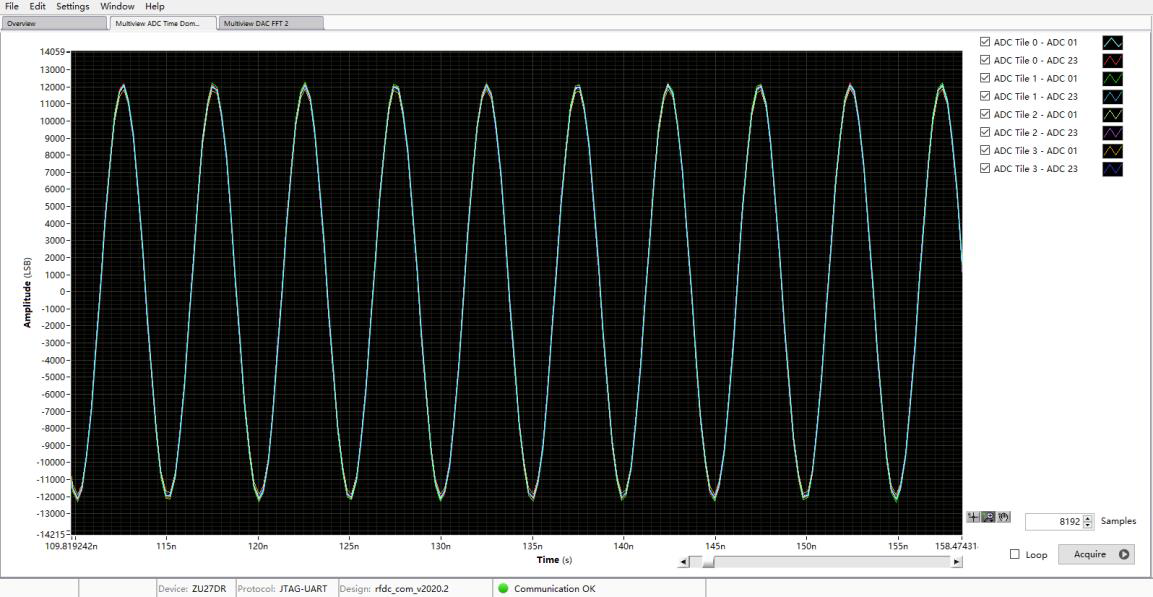

信号源输出800Mhz正玄波,经过功分器转为4路,分别输入至RFSOC 4个不同的TILE中的ADC上。

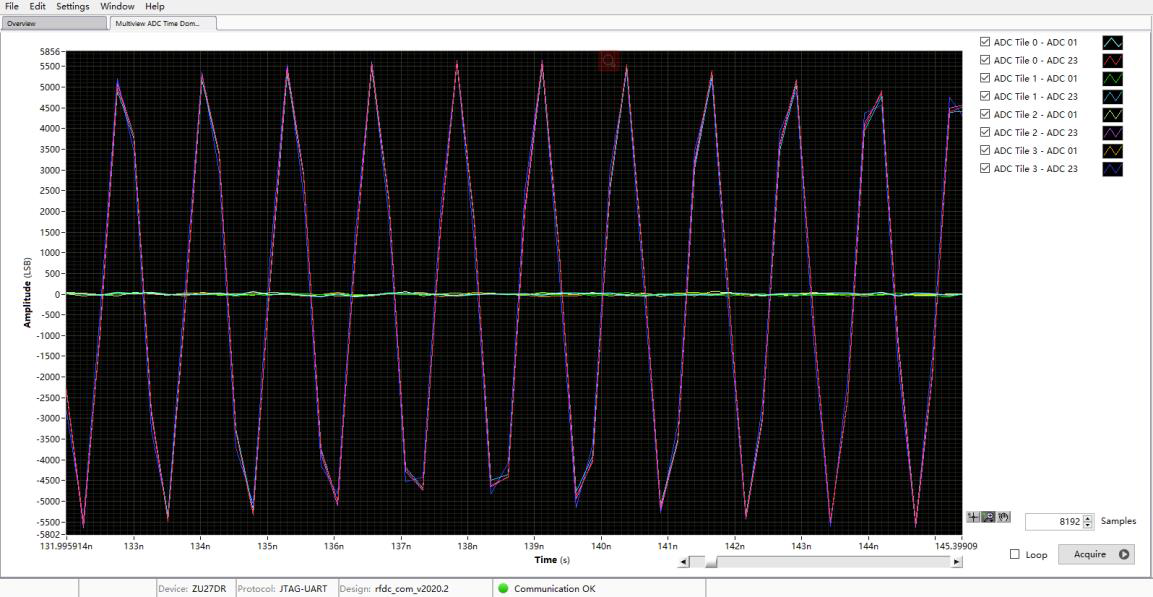

在窗口中可以将8路ADC的采集波形同时绘出,以便观察信号采集的同步性能。

2、DAC同步输出测试

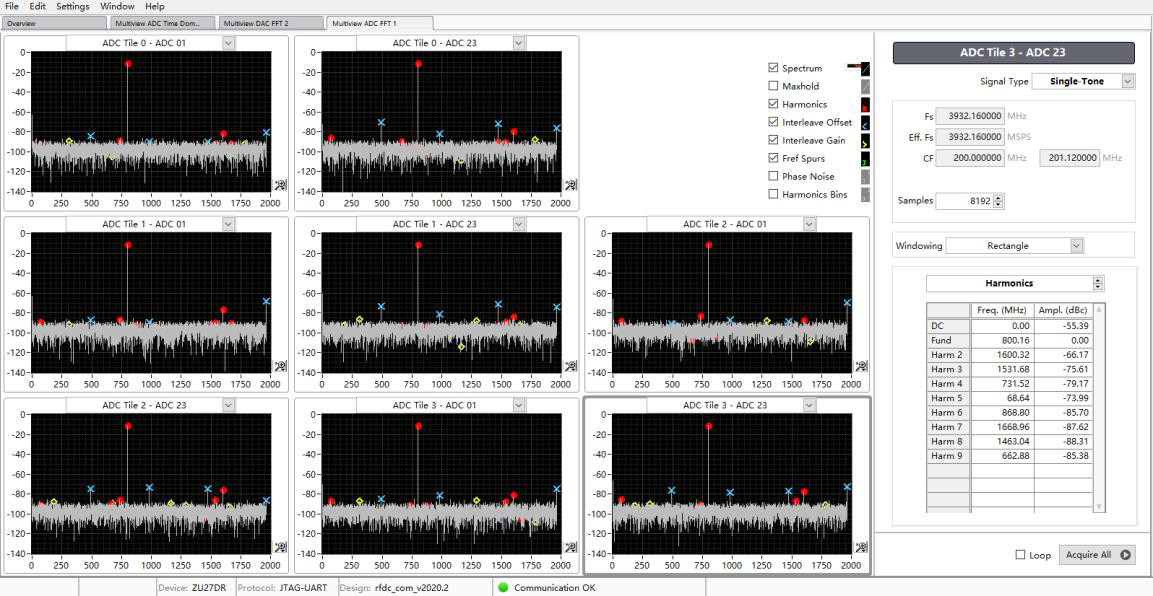

RFSOC设置为DAC同步输出200M单音正玄波信号,板卡进行回环连接线至8路ADC进行同步采集。

在窗口中可以将8路ADC的采集波形同时绘出,以便观察信号采集的同步性能。

提高DAC输出单音正玄波信号至800MHz,板卡进行回环连接线至8路ADC进行同步采集。

在软件上可以使用频域显示8路ADC采集信号对应的FFT结果。

在时域窗口中可以将8路ADC的采集波形同时绘出,以便观察信号采集的同步性能。

四、AD/DA平坦度测试

1、ADC平坦度

(1)100-2000M

外部信号源输出100-2000Mhz扫频信号,ADC进行采集,使用RF Analyzer 进行观察;可见100-2000Mhz频率范围内,ADC采集信号的幅度差在大约3-5dbm之内。

(2)700-1300M

外部信号源输出700-1300Mhz扫频信号,ADC进行采集,使用RF Analyzer 进行观察;可见700-1300Mhz频率范围内,ADC采集信号的幅度差在大约1-2dbm之内。

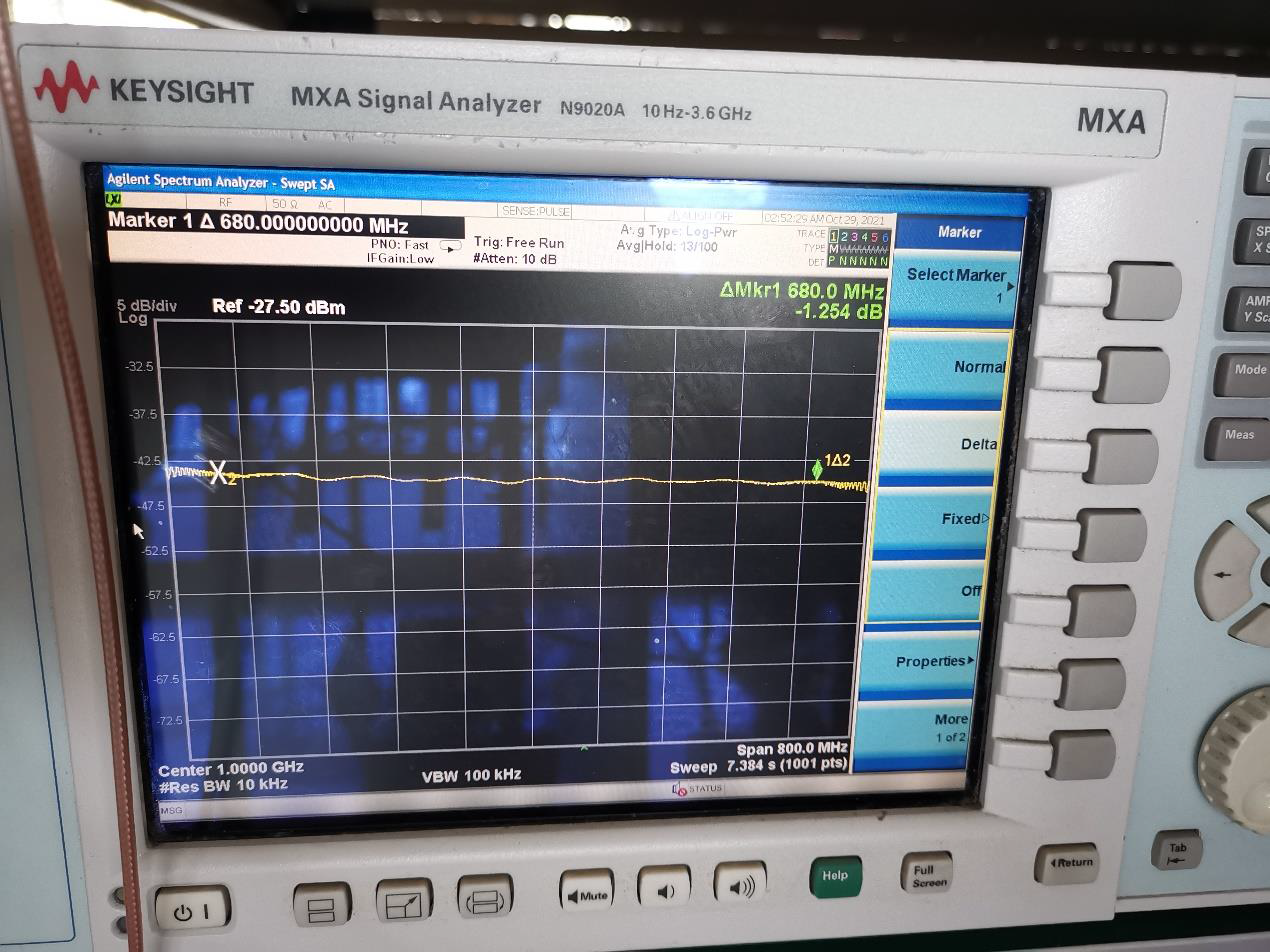

2、DAC平坦度

使用RF Analyzer 输出800M带宽扫频信号,由DAC输出至频谱仪进行观察;可见输出信号幅度差在2dbm之内。

五、AD/DA信号串扰测试

1、ADC串扰测试

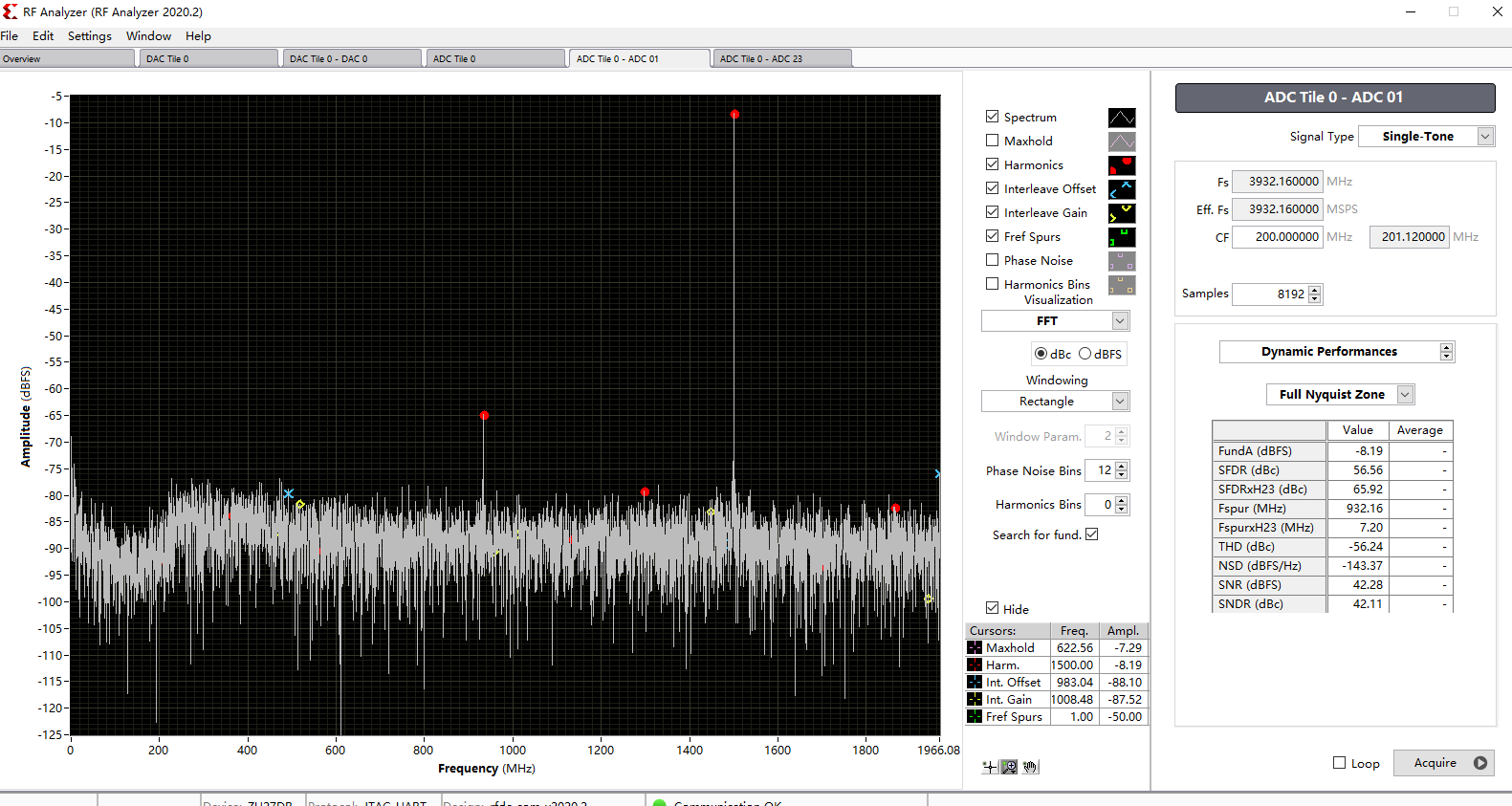

外部信号源输出1500Mhz单音信号,ADC进行采集,使用RF Analyzer 进行观察;

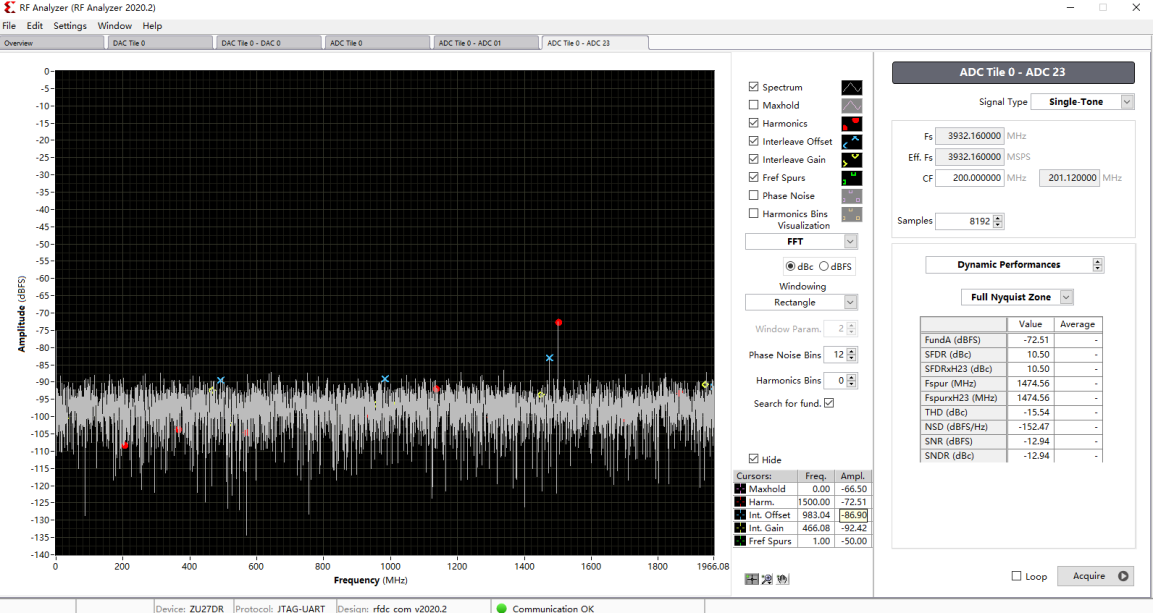

此时相同Tile内其他ADC采集到的信号为:

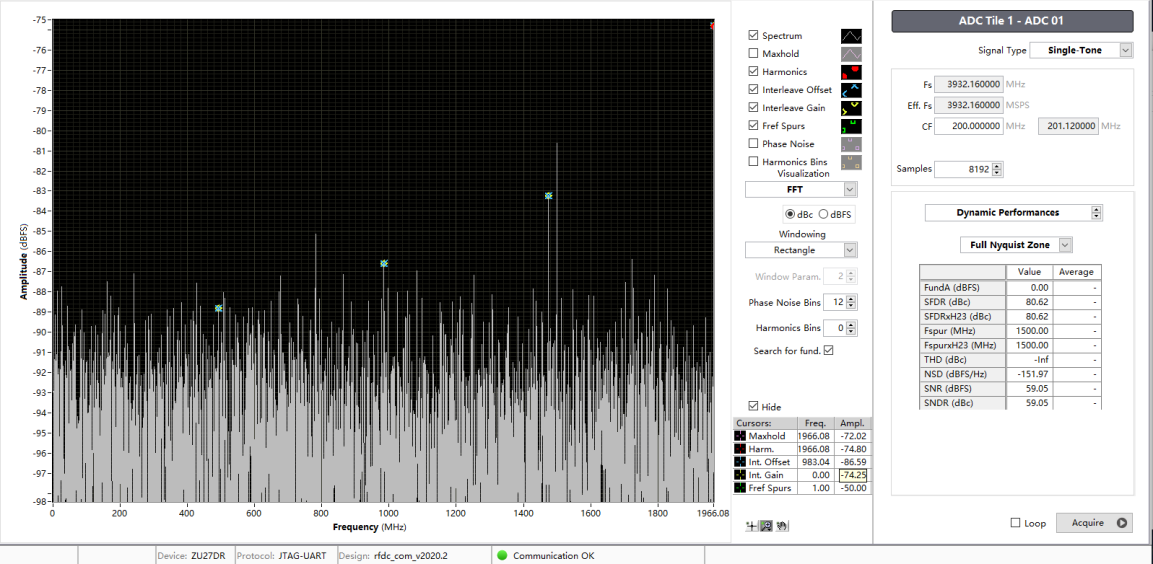

此时其他不同Tile内ADC采集到的信号为:

2、DAC串扰测试

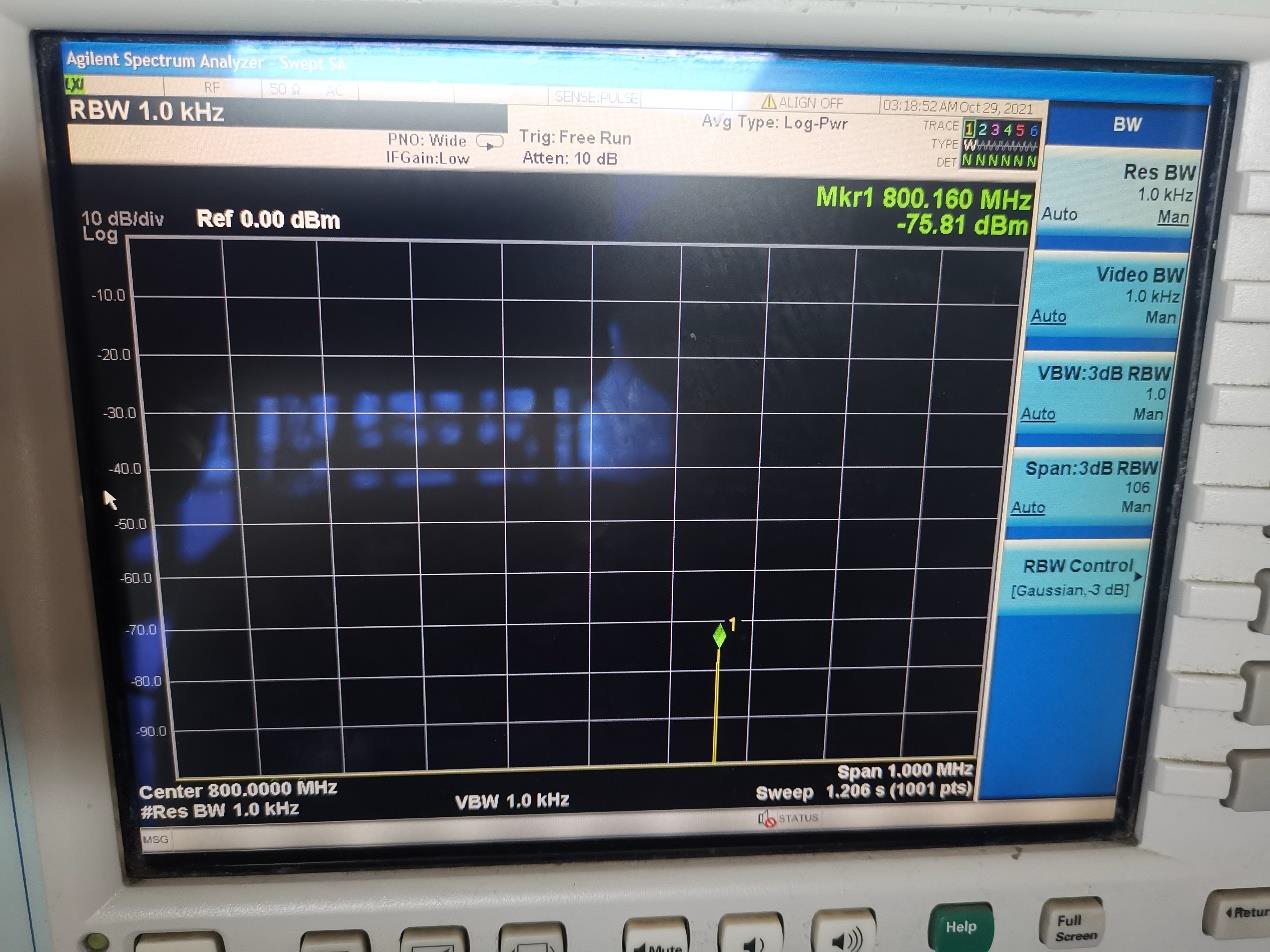

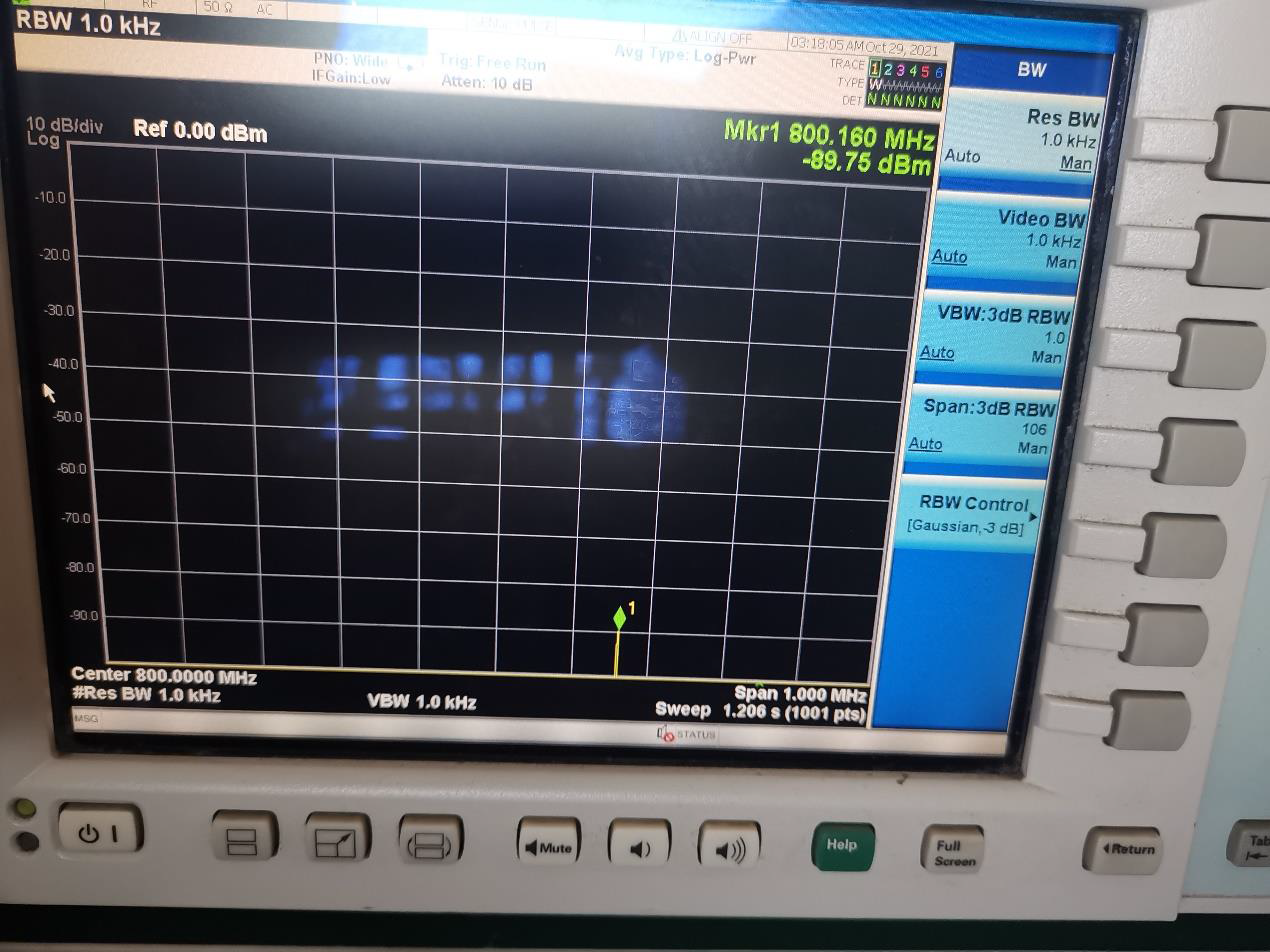

使用RF Analyzer 输出800M单音信号,连接相同Tile内其他DAC至频谱仪进行观察;

使用RF Analyzer 输出800M单音信号,连接其他Tile内DAC至频谱仪进行观察;

六、其他ADC指标测试

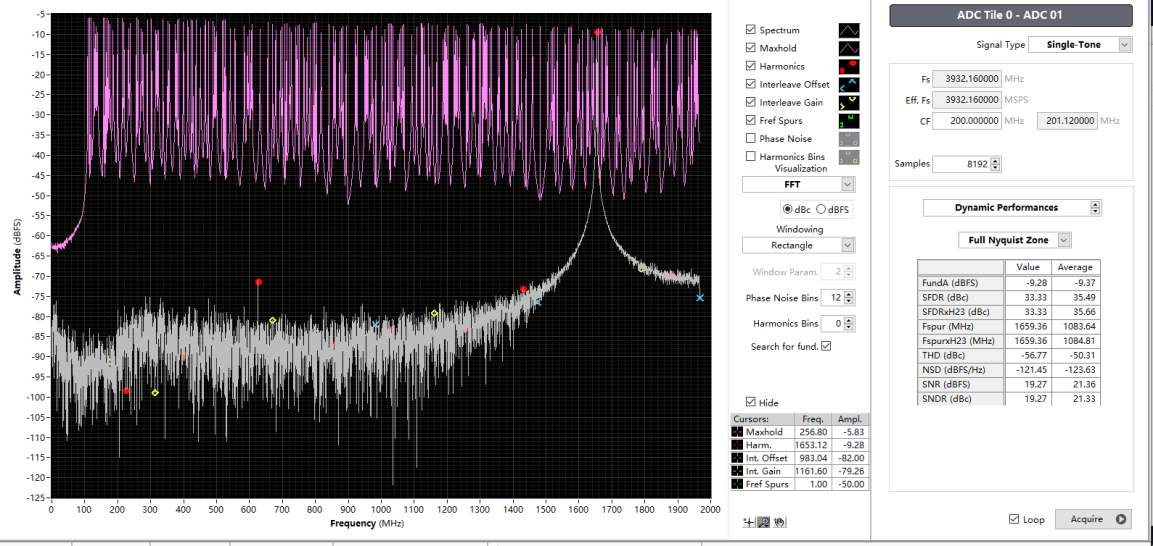

1、无杂散动态范围SFDR

无杂散动态范围 (SFDR) 常用于衡量数据转换器在杂散分量干扰基本信号或导致基本信号失真之前可用的动态范围。SFDR 的定义是基本正弦波信号均方根 (RMS) 值与从 0Hz (DC) 到二分之一数据转换器采样速率 (如 fs/2) 范围内测得的输出峰值杂散信号均方根值之比。峰值杂散分量可以是谐波关系,也可以是非谐波 关系。 无杂散动态范围 (SFDR) 常用于衡量数据转换器在杂散分量干扰基本信号或导致基本信号失真之前可用的动态范围。SFDR 的定义是基本正弦波信号均方根 (RMS) 值与从 0Hz (DC) 到二分之一数据转换器采样速率 (如 fs/2) 范围内测得的输出峰值杂散信号均方根值之比。峰值杂散分量可以是谐波关系,也可以是非谐波关系。 SFDR 可以使用下列方程计算:

或者, SFDR(dBc) = 基本信号幅度 – 最大杂散幅度

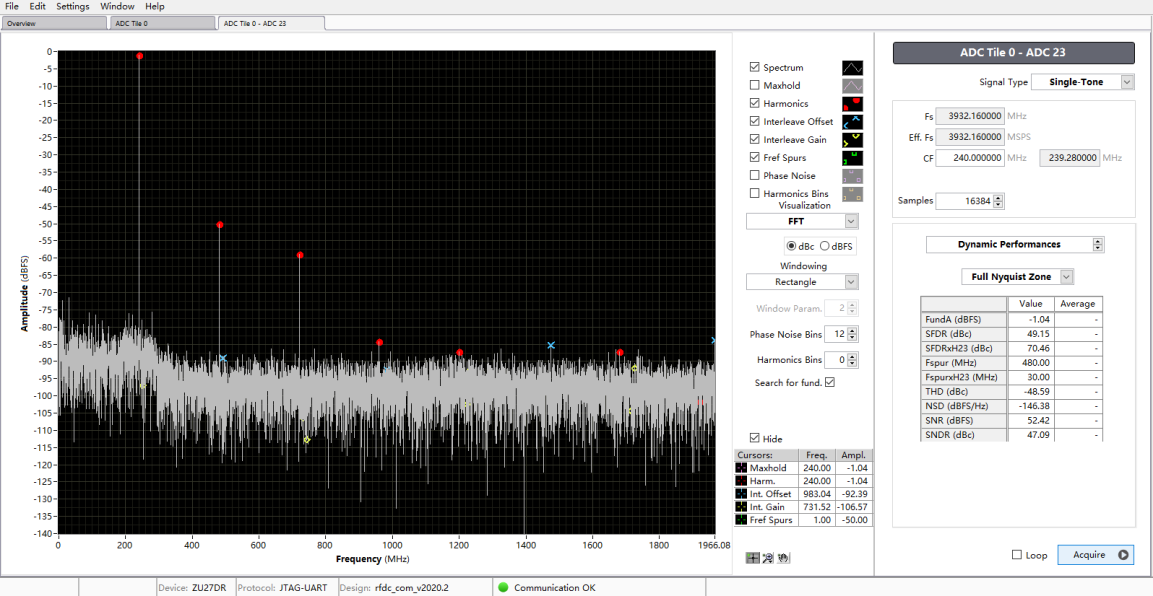

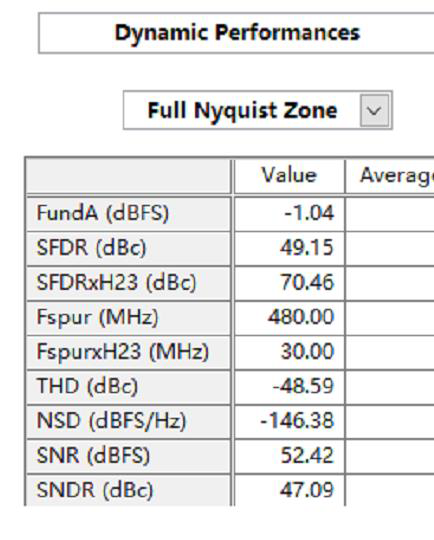

下图所示的是 Zynq UltraScale+ RFSoC 的 RF-ADC 的 SFDR 性能和谐波性能,在 240MHz 输入幅度为–1dBFS 时,测得 SFDR = 49.15dBc。

数据转换器的 SFDR 常常受输入信号的二次或三次 谐波限制,但通过精心设计滤波器和优化频率分配,一般可避免二次谐波 (HD2) 和/或三次谐波 (HD3),大幅提高 SFDR。在排除 HD2 和 HD3 后,图中的 SFDRxH23 是 70.46dBc。

上图中工具也会同时分析出ADC相关指标,如下。

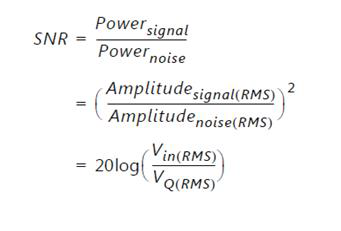

2、信噪比SNR

信噪比 (SNR) 是一般用来量化数据转换器内噪声的参数。它是输入信号功率与噪声功率的比值,一般使用dB 作为单位。类似地,SNR 也能使用信号幅度和噪声幅度的 RMS 值衡量,如方程:

由于采样抖动,信噪比在较高频率下一般会劣化。噪声来自于三个源头:

1. 量化噪声

2. ADC 热噪声

3. 抖动或采样不确定噪声

在满刻度正弦波输入条件下,ADC 的理论最高 SNR 从量化噪声推导而得。在奈奎斯特带宽上,信噪比还 有另一个表达式:

SNR=6.02N+1.76db

这里 N 是理想 ADC 的位数。该公式体现的是对于理想的 N 位数据转换器(不考虑谐波失真)的正弦波输入,整个奈奎斯特带宽上能达到的最佳 SNR。此外,数据转换器的 SNR 也受到自身热噪声和采样时钟相位噪声的限制。当输入信号带宽低于奈奎斯特速率时,SNR 可以得到改善。

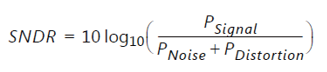

3、信噪失真比SNDR

信噪失真比(也称为 SINAD)指输入正弦波时,RMS 信号功率与 (a) 总噪声功率和 (b) 输出端(不含 DC)的所有其他频率分量功率加上所有其他谐波分量功率的 RMS 和的比值。

SNDR 是用于衡量数据转换器的动态性能的关键参数之一,因为 SNDR 包含奈奎斯特带宽上的所有噪声和杂散。SNDR 说明的是输入信号的质量;SNDR 越大,输入功率中的噪声和杂散比率越小。SNDR的表达式为:

其中,信号功率是有用信号、噪声和失真分量的平均功率。SNDR 一般使用的单位有分贝 (dB)、相对于载 波分贝 (dBc) 或满刻度分贝 (dBFS)。

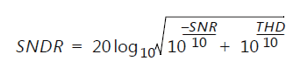

SNDR 也有另一个表达式:

SNDR 是 SNR 规格和 THD 规格的综合,因此,SNDR 将所有不良频率分量与输入频率做比较,从而从总 体上衡量数据转换器的动态性能。

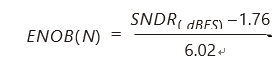

4、有效位数ENOB

有效位数 (ENOB) 是用于衡量数据转换器相对于输入信号在奈奎斯特带宽上的转换质量(以位为单位)的 参数。ENOB 假定转换器是拥有理论上完美性能的转换器。完美数据转换器绝对不发生失真,唯一产生的 噪声是量化噪声,所以 SNR 等于方程 3中的 SNDR,即 SNR(dBFS) = 6.02N + 1.76。因此,ENOB也是指定 SNDR 的另一种表达方式:

其中 SNDR(dBFS) 假定满刻度输入信号。

然而,对于非理想数据转换器而言,SNDR 和 ENOB 会发生劣化,包含噪声和其他缺陷,例如器件热噪声、 输出代码缺失、谐波、AC/DC 非线性、增益/偏移误差和孔径时钟相噪或抖动。外部偏置基准源和电源轨上的噪声也会降低 ENOB。

此外,类似于THD 因非线性原因随输入频率增加而劣化,ENOB值也会随频率加大而劣化。ENOB 来自于 SNDR,而 SNDR 又与 THD 以及 SNR 相关联。要了解数据转换器的准确 ENOB,需阅读数据手册中的详细规格和规定的条件。

鉴于上述标准,大部分模拟数据转换器 IC 厂商一般倾向于推广理想条件下的 ENOB,尤其是数据手册标题所载的 ENOB 值。然而,大量系统工程师和采购经理仍然好奇的是,为什么测量出的 ENOB 值和数据手册所载的理想值不同。有关 ENOB 的一些理解要点:

• 一般数据转换器数据手册标题显示的“位数”(12 位或 14 位)指的是数字位或电压分辨率。这与 ENOB无关。

• ENOB 主要与噪声、非线性和输入频率存在函数关系。

• ENOB 会因多种外部不确定性因素(例如时钟源、电源等)而劣化。

• ENOB 是在整个奈奎斯特带宽上(DC 到 fs/2)计算的。

• ENOB 并非是分析 SDR 等直接 RF 系统的理想指标。

可以咨询我们了解更多设计细节,以及详细的技术方案!也许我们有相似的应用案例。